Studio 2B

Overview

Studio sessions must be done in small groups of 2-4 people. The group work is an important part of the studio experience. You are not required to work with specific students and may adjust groups next week or when we move to a new room. We expect you to be be respectful and professional in your interactions with your peers.

You should ensure that everyone in your group contributes to and benefits from the work.

Artifacts for this studio

Include an answer to questions in the numbered sections in your submission. Include the relevant section number for each answer, like 1.1.

Chapter 2: Gates

Tables

Given the following desired behavior:

| Inputs | Output | ||

|---|---|---|---|

| A | B | C | Y |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

Canonical Form

Create the full, canonical (Sum-of-Products) equation for the output. (Note that inversion can be represented in text with the forward slash, as in /A)

Vs. Minimization of Binary ANDs

Assuming the goal is to minimize the number of items that are “and-ed” together, is the canonical form optimal? If not, provide a more optimal equation and brief explanation of you arrived at it.

Gates & Propagation Delay: Assumption 1

Assuming that AND gates can be arbitrarily wide with no additional delay:

- Sketch the gate level representation of each

- What would be their relative propagation (i.e., which is faster/slower and why do you think this?). You may assume that the propagation delays used in JLS are reasonably representative (5 units of time for invertors and 10 units of time for ANDs).

Propagation Delay: Assumption 2

Assuming instead that only true, binary AND can be done (i.e., 2 inputs). Multi-bit ANDs would have to be accomplished by a sequence of 2-input AND gates.

- Sketch the gate level representation of each

- What would be their relative propagation (i.e., which is faster/slower and why do you think this?). You may assume that the propagation delays used in JLS are reasonably representative (5 units of time for invertors and 10 units of time for ANDs).

Simulation

Download this starter file: studio_2b_113.jls and create a simulation of the canonical equation via JLS. Simulate the behavior for all values shown in the truth table.

Multiplexers

As was discussed in class, multiplexers are well suited to picking between multiple values. Assume that you already have access to multi-input Multiplexers

Using 4-to-1 Multiplexers

Assume that you have a 4-to-1 multiplexer and want to leverage it to create the function shown in the table above (pervious problems). Using A and B as the “selector inputs” to the multiplexer, sketch and describe how you would create a circuit that determines the appropriate value of Y. You will need to use other parts, like a bundle of wires or constants (hover over parts in JLS for the help text).

Using 8-to-1 Multiplexers

Assume that you have an 8-to-1 multiplexer and want to leverage it to create the function shown in the table above (pervious problems). Using A, B, and C as the “selector inputs” to the multiplexer, sketch and describe how you would create a circuit that determines the appropriate value of Y.

Simulation

Download this starter file: studio_2b_23.jls and create a simulation of the 4-to-1 multiplexer imlpementation (from 2.1, not from 2.2) via JLS. Simulate the behavior for all values shown in the truth table.

Getting Glitchy

The book describes a as:

| … a single input transition can cause multiple output transitions. |

(The term “hazard” usually applies to a situation in a circuit where a glitch could occur under the right circumstances. That is, if there’s a hazard, a glitch could occur when the circuit is operating)

Prior Glitches

Did you experience glitches in any of your prior work? If so, review and try to explain why the glitch occurred based on the inputs you used.

An Intentional Glitch

Glitches are normally a by-product of circuits. Where hazards exist, one just needs to ensure that outputs are not used until after sufficient time for all glitches to pass.

Intentionally constructing a circuit and inputs that will demonstrate a glitch can be useful to ensure you understand the causes of glitches.

Download this starter file: studio_2b_32.jls. It includes an input pin, an output pin, two NAND gates, and the Signal Generator is already configured.

Think about how to use the two NAND gates to create a configuration that will demonstrate a glitch with the given input signals:

- BEFORE you actually create and simulate the circuit, explain your reasoning behind your choices and why you think they will cause a glitch.

- THEN test your work and either confirm your thinking or, if it doesn’t confirm your work, try again and explain any errors in your initial reasoning.

Discrete Components & Real Machines

Your lab kit will include several “7400 series” parts:

- 7400: 2-Input NAND gates (Datasheet)

- 7402: 2-Input NOR gates (Datasheet)

- 74151: 8-to-1 Multiplexer (Datasheet)

- 74175: 8-to-1 Multiplexer (Datasheet)

These parts were used extensively in Digital Logic from the 1960s-1980s. They were “packaged” in a plastic rectangle with wire “legs” that became a common symbol for electronics and digital logic, as shown on this tee shirt or here.

Real-World Values

Review the datasheet for the 7400 (link above) and consider it’s real-world properties:

- What is considered a

1(high)? - What is considered a

0? - The part contains 4 NAND gates, but has a total 14 wires. What are the other two used for / why are they needed?

- Consider it’s physical size. If our computer needs 1000 NANDs, estimate how much space may it take up?

Nothing But NANDs

Assume that you have access to only 7400 chips.

- How can you implement other logic functions using only NANDs? Describe how to do “inversion” and AND.

- Sketch how you could complete the circuit from part 1 (the table) using only the 7400 part. (How few 7400 parts would you need?) You can ignore the inputs and outputs for now. Show both the schematic of the logic using NAND gates and a rough sketch of how the 7400 parts need to be used.

Real-World Inputs

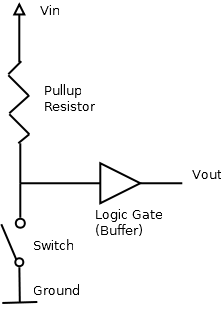

We will use switches and “pull-ups resistors” to avoid unpredictable “floating inputs”

The switch, pull-up resistor, and gate are connected like:

In our case:

-

Vinwill be 5 volts - The resistor will be a 10k Ohm Resistor

The total voltage on the logic gate’s input can be calculated using Ohm’s Law:

- When the switch is open (not connecting), it is an infinite resistance

- When the switch is closed (connecting), it has zero resistance

Thus you can calculate the voltage value at the gate’s input and, using the Datasheet, identify if the value will be considered a 0 or a 1.

How many resistors and switches are needed for your inputs for the previous part?

Update your sketch from the previous part to include the switches and resistors needed for input.

Lights, …

Lab kits also come with several Light Emitting Diodes (Usually just called LEDs). As you may expect from the name, they “emit light”. We’ll be using LEDs to demonstrate the output value from logic. When the LED is on (emitting light) it will represent a 1 and no light will be a 0.

LEDs can burn out if too much current passes through them, so they are usually used in conjunction with a Current Limiting Resistor (another application of Ohm’s Law!).

Update your sketch to include use of an LED and resistor on the output (you can omit the specific value of the resistor, but usually 100-400 $\Omega$ is sufficient).

Challenge (Optional)

Tinkercad is a free, friendly, on-line tool for various types of Computer Aided Design (CAD), including circuits. You can actually build and simulate the circuit you’ve sketched out using parts available in Tinkercad:

- A Breadboard for connecting parts and wires (SparkFun Breadboard Tutorial)

- 7400s

- Resistors

- Switches

- A power supply configured to provide 5 volts

- Wires

Submission / End-of-class

Discuss your work/findings with TAs/instructors. Submit a copy of the questions with everyone’s name at the top (at least one person should submit it, but it’s ok if everyone does).

Submission Link: Canvas