Homework 5

Repository

Create a repository for your assignment via: link

Problem 1

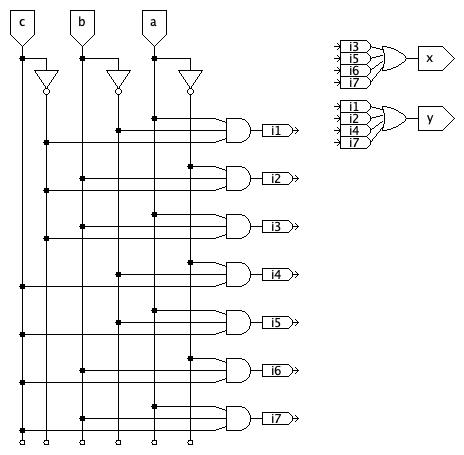

Complete the following circuit in p1.sv (the p1_logic folder) using structural modeling! You can simulate the circuit and should utilize the provided testbench, p1_tb.

Recall from studio that primitive gates can be modeled with the format: type(output, inputs...). For example, a 3-input or gate could be modeled with or(output, a, b, c); or with a unique name for the instance of the or gate, like or gate1(out, a, b, c);.

Caution!

The problem asks for a structural model. You should not use assign or always_comb statements. You should use the primitive parts and(...), or(...), not(...), etc. Although you may pass test cases with other forms of modeling, credit will only be given for a structural model.

Problem 2

32-bit ALU

An Arithmetic Logic Unit is a fundamental part of CPUs. An ALU generally has three inputs and at least one output. Two inputs represent values to be combined by an operation and the third input describes how those values should be combined to produce the output.

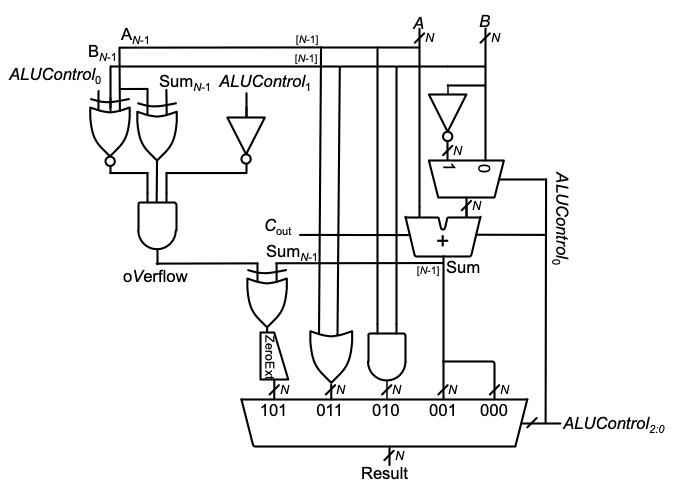

A simplified version of the ALU from chapter 5 (Figure 5.18 b) is:

The behavior of this ALU can be described with the following table:

| ALUControl | Result |

|---|---|

| 000 | A+B |

| 001 | A-B |

| 010 |

A AND B (bitwise and) |

| 011 |

A OR B (bitwise or) |

| 100 | undefined |

| 101 | 1 if “A<B” (signed values), 0 otherwise (using the logic in the diagram) |

| 110 | undefined |

| 111 | undefined |

- A bitwise operation combines corresonding bits of multi-bit values. For example, if

AandBare two-bit numbers, the 0th bit of the bitwise AND would be from ANDing the 0th bits ofAwith the 0th bit ofB. The 1st bit of the bitwise AND would be from anding the 1st bits ofAandB, etc. - “Less than” can be determined by either (but not both) a negative result from

(a-b)or if(a-b)results in overflow. You can use the exact logic shown in the diagram - All

undefinedcontrol values should leave theresultas 0.

Hints

- Verilog’s

if/elseorcasestatements (both described in chapter 4) are great choices for most of what ALUs need to do. - Bit subscripting (

[]) and bit swizzling (book examples 4.12 in section 4.2.9) are useful here!

Complete the alu in the p2_alu folder (Create a 32-bit ALU. That is, $N=32$). You can simulate the model and should use the provided testbench, alu_tb.sv.

More Hints

Develop Incrementally! Do on or two operations and use the simulator to review your work/progress.

Problem 3

More Soda!

Below is a slightly updated version of the soda machine from homework 3!

You have been enlisted to redesign a soda machine dispenser for your department lounge. Sodas are partially subsidized by the student chapter of the IEEE, so they cost only 25 cents. The machine accepts nickels, dimes, and quarters. When enough coins have been inserted, it dispenses the soda and returns any necessary change. Design an FSM controller for the soda machine. The FSM inputs are clk, reset, nickel, dime, and quarter. The outputs are dispense,return_nickel, return_dime, and return_two_dimes. When the FSM reaches 25 cents, it asserts Dispense and the necessary Return outputs required

to deliver the appropriate change. Then, it should be ready to start accepting coins for another soda.

Implement this state machine in p3/soda.sv with the following updates:

-

resetshould be an asynchronous reset (posedge resetis included in the sensitivity list for the flip-flops) - Do a behavioral implementation (

assignstatments,always_...blocks, etc.) - Test cases include clock cycles with no active inputs (no additional coins being added).

- As before, you may assume that there will be no coins added when dispensing or returning coins.

A test bench (and corresponding task to run it) has been provided for you. (The test bench assumes that your state machine has an asynchronous reset!)

Hint

Verilog’s if statement, which was included in several examples in Chapter 4, is useful.

Complete the state machine for the soda dispenser, soda.sv, in the p3_soda folder. Again, you can simulate the circuit and you should use the provided testbench, soda_tb.sv.

Problem 4

Answer the questions in the question.md in the designated places (remove / replace the TODO lines)

Submission

The assignment will be submitted via GitHub and Gradescope.

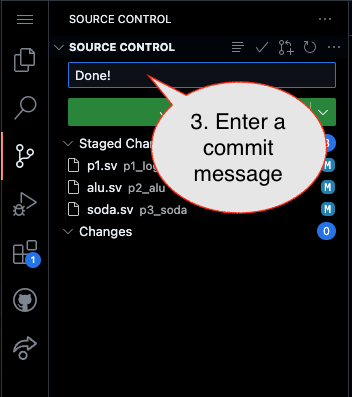

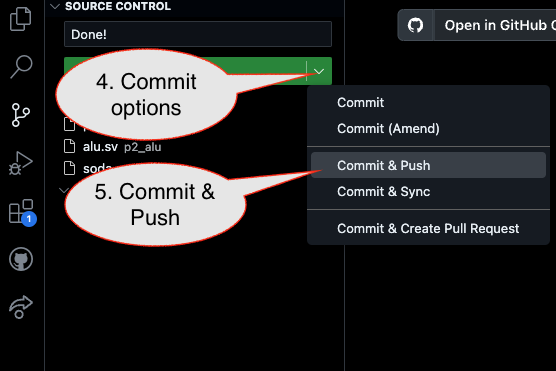

1. First, be sure to commit and push files to GitHub (as shown in studio)

1.1

1.2

1.3

2. Then go to GitHub.com and confirm the updates are on GitHub

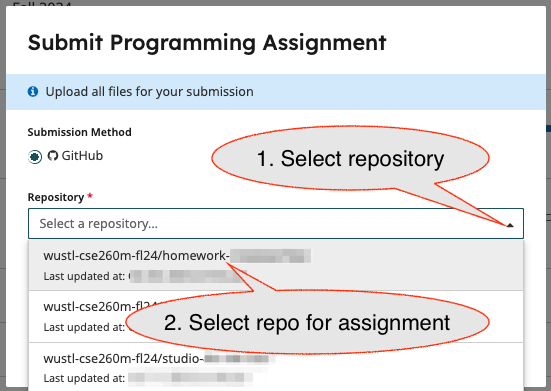

3. Finally (after confirming updates are on GitHub), go to the assignment in Gradescope and import it from GitHub:

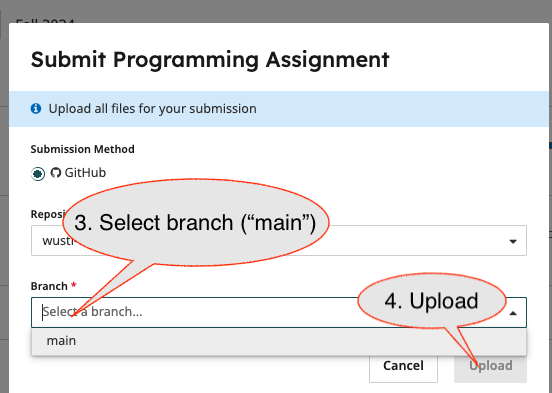

3.1

3.2